## Communication

# Organic Nanodielectrics for Low Voltage Carbon Nanotube Thin Film Transistors and Complementary Logic Gates

Seung-Hyun Hur, Myung-Han Yoon, Anshu Gaur, Moonsub Shim, Antonio Facchetti, Tobin J. Marks, and John A. Rogers

*J. Am. Chem. Soc.*, **2005**, 127 (40), 13808-13809• DOI: 10.1021/ja0553203 • Publication Date (Web): 17 September 2005 Downloaded from http://pubs.acs.org on March 25, 2009

# More About This Article

Additional resources and features associated with this article are available within the HTML version:

- Supporting Information

- Links to the 18 articles that cite this article, as of the time of this article download

- Access to high resolution figures

- Links to articles and content related to this article

- Copyright permission to reproduce figures and/or text from this article

View the Full Text HTML

Published on Web 09/17/2005

### Organic Nanodielectrics for Low Voltage Carbon Nanotube Thin Film Transistors and Complementary Logic Gates

Seung-Hyun Hur,<sup>†</sup> Myung-Han Yoon,<sup>‡</sup> Anshu Gaur,<sup>†</sup> Moonsub Shim,<sup>†</sup> Antonio Facchetti,<sup>‡</sup> Tobin J. Marks,<sup>\*,‡</sup> and John A. Rogers<sup>\*,†</sup>

Department of Materials and Science Engineering, Chemistry, Beckman Institute, Frederick and Seitz Materials Research Laboratory, University of Illinois, Urbana, Illinois 61801, and Department of Chemistry and the Materials Research Center, Northwestern University, 2145 Sheridan Road, Evanston, Illinois 60208

Received August 12, 2005; E-mail: jrogers@uiuc.edu; t-marks@northwestern.edu

Aligned arrays and random networks of single-walled carbon nanotubes (SWNTs) represent thin film material types that are attractive as conducting/semiconducting elements of flexible electronic circuits.1 The large carrier mobilities2 and mechanical, chemical, and electrical robustness<sup>3,4</sup> of individual SWNTs imbue these films with remarkably good properties. However, highperformance thin film transistors (TFTs) using submonolayer SWNT films (arrays or networks) as the semiconductor<sup>5</sup> require high capacitance gate dielectrics to enable low voltage and possibly hysteresis-free operation. For complementary circuits, this dielectric must also be compatible with polymer coatings and other chemistries enabling unipolar n- or p-channel transport in SWNT TFTs.67 Flexible electronic devices require the dielectric to be mechanically bendable; for systems that use plastic substrates, the ability to deposit the dielectric from solution at low temperatures is also important. Developing materials that satisfy all of these requirements is challenging. Thin liquid polymer electrolyte films provide gates and gate dielectrics that have some of these characteristics and were recently used with SWNTs to achieve TFTs with good properties.8 However, drawbacks of this approach include long response times  $(\sim 1-10 \text{ ms})$  associated with electrolyte migration and difficulties in integrating thin liquid layers into complex circuits. We report here that nanoscopic 3-D  $\sigma$ - $\pi$  self-assembled superlattices (SASs) function as exceptionally good dielectrics for n- and p-channel SWNT TFTs. The excellent performance characteristics of these devices and of complementary logic gates formed with them suggest that dielectrics of this general type offer a promising path to SWNTbased thin film electronics.

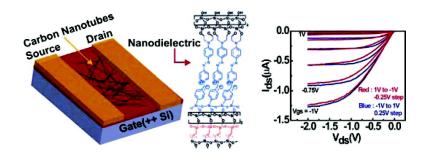

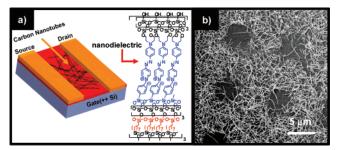

Figure 1a illustrates the device layout which includes patterned metal source and drain electrodes, a random SWNT network for the semiconductor, and a SAS multilayer for the dielectric, here on a doped silicon wafer serving as substrate and back gate. The SAS nanodielectric multilayer was deposited via solution methods describe previously.<sup>9</sup> This nanodielectric has a thickness of  $\sim 16$ nm and a capacitance of  $170 \pm 9 \text{ nF/cm}^2$  ( $10^3 - 10^6 \text{ Hz}$ ), as measured by impedance spectroscopy. Transfer printing techniques placed networks of SWNTs grown by chemical vapor deposition (CVD) on SiO<sub>2</sub>/Si wafers directly onto the SAS nanodielectric.<sup>4</sup> The CVD growth conditions can be adjusted to achieve a relatively high SWNT coverage ( $\sim$ 30 tubes/ $\mu$ m<sup>2</sup>).<sup>7</sup> Figure 1b shows scanning electron micrographs (SEMs) of such SWNT networks transfer printed from CVD growth substrate onto the SAS nanodielectric layer. The tube density per unit area is similar in the two cases, consistent with the high transfer printing process efficiency. The holes visible in the transferred networks represent an artifact of the procedures used here and have near-negligible influence on

*Figure 1.* (a) Schematic illustration of a thin film transistor that uses a large number of individual SWNTs as an effective semiconducting "film" and a nanoscale SAS as the gate dielectric. (b) Scanning electron micrographs of single-walled carbon nanotube networks transfer printed from the CVD growth substrate onto the SAS nanodielectric layer (thickness  $\sim$ 16 nm)/Si.

device performance. AFM (Supporting Information) suggests that the transferred SWNTs rest on the top surface of the dielectric and are not substantially pressed into it during transfer. SWNT–SAS adhesion, which is likely van der Waals in origin, leads to bonding sufficiently strong to pass "Scotch tape" tests. This good adhesion together with the robustness of the dielectric allows direct photolithographic patterning of source and drain electrodes by liftoff.

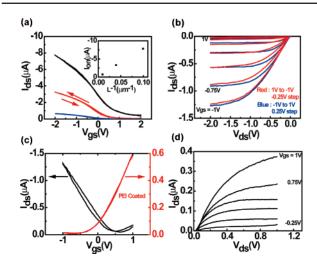

Figure 2 shows the current-voltage response of typical TFTs having the present design. As fabricated, and in ambient, they exhibit unipolar p-channel operation with moderate, positive threshold voltages and little hysteresis. This latter property is in sharp contrast to the behavior of devices that use a 100 nm SiO<sub>2</sub> layer as the dielectric (Supporting Information). In this case, large hysteresises, corresponding to 10-20 V shifts in threshold voltage, are observed in ambient, depending on the direction and range of gate voltage sweeps. This marked hysteresis, also present in single tube devices,10 declines with decreasing SiO2 thickness and decreasing gate voltage,11 but still presents problems for operation of such devices in circuits, even with SiO<sub>2</sub> thicknesses in the 20 nm range (Supporting Information). Some work suggests that the hysteresis arises from charge injection into traps in the dielectric, especially at high gate voltages and when there is adsorbed water near the SWNTs.<sup>10</sup> Reports of high  $k^{12}$  and ultrathin dielectric layers<sup>13</sup> exist, but few describe hysteresis in detail. Since fixed positive charges, interface state densities, and the surface chemistries of the SAS nanodielectric are similar to those of SiO<sub>2</sub>,<sup>9</sup> we speculate that the low hysteresis is derived mainly from the low operating voltages enabled by the high capacitance. Devices using the SAS dielectric grown on a 100 nm SiO2 layer exhibit hysteresis comparable to that in devices with SiO2 alone (Supporting Information).

Low hysteresis allows accurate measurement of both linear and saturation regime behavior. By using a series model of the dielectric

<sup>&</sup>lt;sup>†</sup> University of Illinois. <sup>‡</sup> Northwestern University.

**Figure 2.** Plot of drain/source current  $(I_{ds})$  as a function of gate voltage  $(V_{gs})$  at a fixed drain/source voltage  $(V_{ds})$  of -0.5 V collected from singlewalled carbon nanotube TFTs using a SAS nanodielectric (a). The devices have channel widths (W) of 200  $\mu$ m and varied channel lengths (L: blue, 100  $\mu$ m; red, 25  $\mu$ m; black, 10  $\mu$ m). The data in the inset of (a) are consistent with the expected linear scaling of the maximum drain/source current ( $I_{ds}$ ), denoted  $I_{ON}$  with  $L^{-1}$ . Plot of  $I_{ds}$  versus  $V_{ds}$  at different gate/source voltages ( $V_{gs}$ ) collected from devices using a SAS nanodielectric (b). Plot of drain/ source current  $I_{ds}$  as a function of  $V_{gs}$  at  $V_{ds} = -1.5$  V before (black) and 1 V after PEI coating (red) (c). Plot of  $I_{ds}$  versus  $V_{ds}$  at different  $V_{gs}$  collected after PEI coating (d). Device in (b–d) have  $L = 100 \ \mu$ m and  $W = 200 \ \mu$ m.

capacitance  $(C_G)$  and the quantum capacitance  $(C_Q)$  of SWNTs according to  $C_{\rm T} = (1/C_{\rm G} + 1/C_{\rm Q})^{-1}$ , and  $C_{\rm G} \approx 170 \text{ nF/cm}^2$ ,  $C_{\rm Q} \approx$ 100-400 nF/cm,<sup>2,8</sup> we estimate the total capacitance ( $C_T$ ) to be  $\sim$ 60–120 nF/cm<sup>2</sup>. (Note that this estimate does not include fringing fields around the SWNT, which can be significant, especially at low tube densities.) Analysis using standard models yields effective device mobilities in the linear and saturation regimes of  $\sim$ 5.6  $\pm$ 0.5 and 5.5  $\pm$  0.4 cm<sup>2</sup>/V·s, respectively, for the devices studied here (tube densities  $\sim 10$  tubes/ $\mu$ m<sup>2</sup>). (Mobilities as high as 30  $\pm$ 5 cm<sup>2</sup>/V·s are achieved at densities of  $\sim$ 20 tubes/ $\mu$ m<sup>2</sup>, but these devices have correspondingly lower on/off ratios.) The similarity of these quantities and the linear scaling of output current with 1/(channel length) (Figure 2a, inset) are consistent with device operation that is not limited by contacts in the present range of channel lengths. The threshold voltages in the linear and saturation regimes are  $0.2 \pm 0.05$  and  $0.3 \pm 0.05$  V, respectively, and do not vary substantially with channel length. The high capacitance of the dielectric and the good mobility lead to high transconductances of 15  $\mu$ S at  $V_{\rm ds} = -2$  V for 10  $\mu$ m channel length. The gate leakage current is ~10 nA at  $V_{gs} = -1$  V.

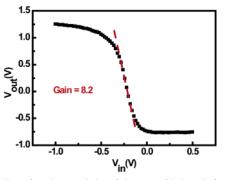

The SAS nanodielectric is also compatible with polymer coating chemistries that switch SWNT TFTs from unipolar p- to unipolar n-channel operation. Thus, a thin layer of polyethyleneimine (PEI,  $M_n = 800$ ) was cast onto the channel regions of the devices, and Figure 2 shows typical n-channel electrical characteristics. Very low hysteresis is again observed, with mobilities and threshold voltages of ~4.1 ± 0.5 cm<sup>2</sup>/V·s and  $-0.2 \pm 0.05$  V, respectively. Combining n- and p-channel transistors on a single substrate can yield integrated complementary logic devices. As a simple example, Figure 3 illustrates typical transfer curves of a SWNT/SAS inverter. The high SAS capacitance and good mobilities lead to gains (~8) that significantly exceed those previously reported for similar SWNT TFT logic gates using SiO<sub>2</sub> dielectrics (100 nm thickness).<sup>7</sup>

In conclusion, we have demonstrated that nanoscopic organic multilayers serve as excellent gate dielectrics for thin film transistors

**Figure 3.** Transfer characteristic of inverter fabricated from p- and n-channel SWNTs/SAS TFTs. Channel length and width are 100 and 200  $\mu$ m, respectively.

using SWNT semiconductors. These results, coupled with emerging approaches to improve current on/off ratios in SWNT TFTs by eliminating the effects of metallic tubes, suggest the potential importance of new carbon-based electronic materials for highperformance logic circuits, displays, and other systems, especially on plastic substrates.

Acknowledgment. We thank T. Banks for help with the processing. This work was supported at UIUC by the DARPA/ AFRL Macroelectronics Program Contract FA8650-04-C-7101, DOE (Grant DEFG02-91-ER45439), and NSF (Grant NIRT-0403489), and at NWU by the NASA Institute for Nanoelectronics and Computing (NCC2-3163) and DARPA/ARO (W911NF-05-0187).

**Supporting Information Available:** AFM image of transferred SWNTs on nanodielectric and hysteresis behavior of SWNTs/SiO<sub>2</sub> (20 and 100 nm) devices. This material is available free of charge via the Internet at http://pubs.acs.org.

#### References

- (a) Artukovic, E.; Kaempgen, M.; Hecht, D. S.; Roth, S.; Gruner, G. *Nano Lett.* **2005**, *5*, 757–760.

(b) Saran, N.; Parikh, K.; Suh, D. S.; Munoz, E.; Kolla, H.; Manohar, S. K. J. Am. Chem. Soc. **2004**, *126*, 4462–4463.

- (2) Durkop, T.; Getty, S. A.; Cobas, E.; Fuhrer, M. S. Nano Lett. 2004, 4, 35–39.

- (3) Yao, Z.; Kane, C. L.; Dekker, C. *Phys. Rev. Lett.* 2000, *84*, 2941–2944.

(4) Hur, S. H.; Park, O. O.; Rogers, J. A. *Appl. Phys. Lett.* 2005, *86*, 243502 1–3.

- (5) (a) Snow, E. S.; Novak, J. P.; Campbell, P. M.; Park, D. *Appl. Phys. Lett.* 2003, *82*, 2145–2147. (b) Hu, L.; Hecht, D. S.; Gruner, G. *Nano Lett.* 2004, *4*, 2513–2517. (c) Zhou, Y.; Gaur, A.; Hur, S. H.; Kocabas, C.; Meitl, M. A.; Shim, M.; Rogers, J. A. *Nano Lett.* 2004, *4*, 2031–2035. (d) Kocabas, C.; Hur, S. H.; Gaur, A.; Meitl, M. A.; Shim, M.; Rogers, J. A. *Small* 2005, in press.

- (6) (a) Javey, A.; Wang, Q.; Ural, A.; Li, Y. M.; Dai, H. Nano Lett. 2002, 2, 929–932. (b) Derycke, V.; Martel, R.; Appenzeller, J.; Avouris, Ph. Nano Lett. 2001, 1, 453–456. (c) Shim, M. Javey, A.; Kam, N. W. S.; Dai, H. J. Am. Chem. Soc. 2001, 123, 11512–11513.

- (7) Hur S. H.; Kocabas, C.; Gaur A.; Park, O. O.; Shim M.; Rogers, J. A. J. Appl. Phys. 2005, in press.

- (8) Ozel, T.; Gaur, A.; Rogers, J. A.; Shim, M. Nano Lett. 2005, 5, 905– 911.

- (9) Yoon, M. H.; Facchetti, A.; Marks, T. J. Proc. Natl. Acad. Sci. U.S.A. 2005, 102, 4678–4682.

- (10) Kim, W.; Javey, A.; Vermesh, O.; Wang, O.; Li, Y. M.; Dai, H. J. Nano Lett. 2003, 3, 193–198.

- (11) Radosavljevic, M.; Freitag, M.; Thadani, K. V.; Johnson, A. T. *Nano Lett.* 2002, 2, 761–764.

- (12) Javey, A.; Kim, H.; Brink, M.; Wang, Q.; Ural, A.; Guo, J.; McIntyre, P.; McEuen, P.; Lundstrom, M.; Dai, H. J. Nat. Mater. 2002, 1, 241– 246.

- (13) Wind, S.; Appenzeller, J.; Martel, R.; Derycke, V.; Avouris, P. Appl. Phys. Lett. 2002, 80, 3817–3819.

JA0553203